## ISTITUTO NAZIONALE DI RICERCA METROLOGICA Repository Istituzionale

Resistive Switching in High-Density Nanodevices Fabricated by Block Copolymer Self-Assembly

This is the author's submitted version of the contribution published as:

Resistive Switching in High-Density Nanodevices Fabricated by Block Copolymer Self-Assembly / Frascaroli, J; Brivio, S; Lupi, F. F.; Seguini, G; Boarino, Luca; Perego, M; Spiga, S.. - In: ACS NANO. - ISSN 1936-0851. - 9:3(2015), pp. 2518-2529. [10.1021/nn505131b]

Availability:

This version is available at: 11696/31836 since:

Publisher:

American Chemical Society

Published

DOI:10.1021/nn505131b

Terms of use:

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright American Chemical Society (ACS)

Copyright © American Chemical Society after peer review and after technical editing by the publisher. To access the final edited and published work see the DOI above.

(Article begins on next page)

# High-Density Resistive Switching Devices Fabricated by Block Copolymer Self-Assembly

Jacopo Frascaroli,<sup>†, ‡,\*</sup> Stefano Brivio,<sup>†</sup> Federico Ferrarese Lupi,<sup>†</sup> Grazia Tallarida,<sup>†</sup> Gabriele Seguini,<sup>†</sup> Luca Boarino,<sup>‡</sup> Michele Perego,<sup>†</sup> and Sabina Spiga<sup>†</sup>

#### **AUTHOR ADDRESS**

†Laboratorio MDM, IMM-CNR, Via C. Olivetti 2, 20864 Agrate Brianza (MB), Italy.

‡INRiM, NanoFacility, Electromagnetism Division, Strada delle Cacce 91, 10135 Torino, Italy

\*Department of Physics, Università degli studi di Milano, Via Celoria 16, 20133 Milano, Italy

KEYWORDS resistive switching, ReRAM, high-density array, HfO<sub>2</sub>, cross-talk, bottom-up fabrication, block copolymer, self-assembly

ABSTRACT Bipolar resistive switching memories based on metal oxides offer a great potential in terms of simple process integration, memory performance, and scalability. In view of ultra-high-density memory applications, a reduced device size is not the only requirement, as the distance between different devices is a key parameter. By exploiting a bottom-up fabrication approach based on block copolymer self-assembling, we obtained the parallel production of bilayer Pt/Ti top electrodes arranged in periodic arrays over the HfO<sub>2</sub>/TiN surface, building memory devices with a diameter of 28 nm and a density of 5·10<sup>10</sup> devices/cm<sup>2</sup>. For an electrical characterization,

the sharp conducting tip of an atomic force microscope was adopted for a selective addressing of the nanodevices. The presence of devices showing higher conductance in the initial state was directly connected with scattered leakage current paths in the unpatterned oxide film. With bipolar voltage operations, we obtained reversible set/reset transitions irrespective of the conductance variability in the initial state, and the high density of the produced electrodes allowed us to detect a cross-talk between different devices occurring during both set and reset transitions, which poses a scalability issue for ultra-high density memory applications.

#### INTRODUCTION

Bottom-up nanofabrication approaches based on block copolymer (BCP) self-assembly offer the possibility to generate high-density features at nanoscale.<sup>1,2</sup> The exploitation of this key-enabling technology for the fabrication of high-density arrays of nanostructured resistive switching devices has not been investigated in detail. Indeed, resistive switching memories (ReRAM) are among the main candidates for future solid-state memory applications able to satisfy the increasing demands in terms of data storage capacity, low power consumption and fast accessing time.<sup>3-5</sup> Resistive switching (RS) devices consist of two terminals capacitor-like structures in which the electrical resistance of the system can be reversibly switched between two (or more) non-volatile values with the application of a potential difference between the two metal electrodes. 6 In a variety of materials, the RS mechanism can be explained in terms of formation of a filamentary conductive path bridging the two electrodes in the low resistance state (LRS) during the set operation, while in the reset process the filament is partially disrupted, leading to the high resistance state (HRS).<sup>7,8</sup> Usually, the switching is initiated by a unique forming process which is responsible for the first establishment of the conductive filament. Due to the small filament size, filament-based RS memories are particularly suited for scaling. In particular, transition metal oxides are among the

main candidates as dielectric materials in future RS memories.<sup>9</sup> HfO<sub>2</sub> is increasingly becoming a model example, since it offers excellent CMOS process integration capability and promising memory performances.<sup>10,11</sup> Recent reports revealed sub-10 nm conductive channel diameter in HfO<sub>2</sub>-based RS devices<sup>12,13</sup> and well-functioning nanoscale devices have been fabricated using either electron beam lithography or a three-dimensional stacking procedure.<sup>14–16</sup> However, these fabrication methods allow the definition of a limited number of memory cells, while the scalability limit of high-density packing has not been explored.

In this view, block copolymer (BCP) thin films demonstrated the ability to self-assemble in periodic nanodomains that can be exploited for the fabrication of nanoscale features, often in combination with current top-down patterning technologies. <sup>1,17,18</sup> This high throughput patterning technique offers the advantage of producing ultra-high density devices, yet maintaining a good control over the device size and spacing as a function of the polymer molecular weight. <sup>19,20</sup> BCPs allow the definition of regular patterns with dimension and spacing that easily go beyond the limits of current optical lithography<sup>21</sup>, and have been used for the formation of complex patterns in different applications such as FinFET transistors, circuit interconnects, capacitors, and charge trapping memories. <sup>22–24</sup> BCPs have also been employed in the fabrication of phase change memories for a reduction of the electrode contact area, achieving a significant power reduction. <sup>25</sup> RS device top electrode downscaling using BCP in combination with electron beam lithography has been reported, in which the BCP was applied to define narrow but isolated features. <sup>26</sup>

In this work, we employ a BCP-assisted lithographic process for the parallel fabrication of nanosized, high-density metal electrodes organized in regular arrays over the HfO<sub>2</sub> switching material. With the conductive tip of an atomic force microscope (C-AFM), we achieve a selective

addressing of the single nanodevices, in order to obtain the switching phenomenon at the nanoscale and investigate the effect of density upscaling on the system properties.

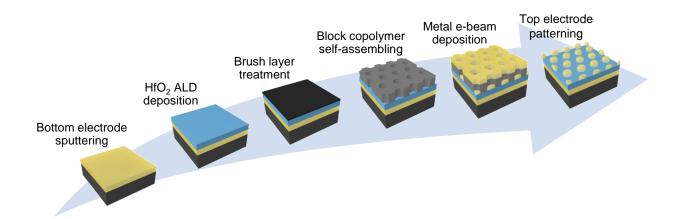

**Figure 1.** Procedure for the top electrode patterning. A BCP self-assembled template was adopted for pattern transfer with a lift-off process.

#### RESULTS AND DISCUSSION

Fabrication of nanoscale RS devices with BCP template

Figure 1 summarizes the adopted process workflow to obtain an ordered array of RS devices by BCP lithography. The first step consists in the sputter deposition of the TiN bottom electrode, followed by the atomic layer deposition (ALD) of a 3 nm HfO<sub>2</sub> film and finally by the Pt/Ti top electrode nanopatterning. This final step employs a lift-off process with a nanoporous template formed by BCP self-assembling. 19,20,27,28

Before BCP deposition, the oxide surface was functionalized with a brush layer of P(S-r-MMA) random copolymer, which is necessary in order to remove the poly(methyl methacrylate) (PMMA) preferential wetting of the surface and obtain a perpendicular orientation of the cylindrical nanodomains in the above BCP layer.<sup>29,30</sup>

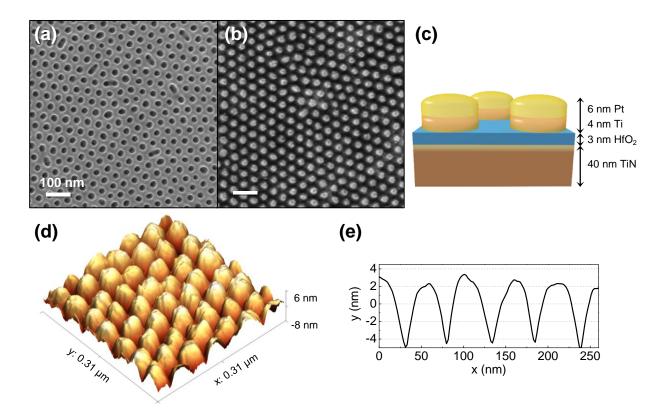

The BCP phase separation was induced with a rapid thermal processing (RTP) heat treatment that allowed a short processing time of 5 minutes.<sup>31,32</sup> We employed a PS-b-PMMA block copolymer with PS content of 70%, obtaining PMMA cylindrical nanodomains with hexagonal periodic distribution within the polystyrene (PS) matrix. Upon selective removal of the PMMA polymeric component, a nanoporous PS periodic structure was obtained, as shown in the SEM image of Figure 2a. The BCP lithographic technique offers the possibility of a fine tuning of the device size and spacing as a function of the polymer molecular weight (M<sub>w</sub>).<sup>33</sup> By employing a M<sub>w</sub> of 102 kg/mol, we obtained devices with a diameter of 28±1 nm and 47±1 nm center-to-center distance, which resulted in an average spacing between neighboring devices of 19±1 nm and a density of 5x10<sup>10</sup> devices/cm<sup>2</sup>. The Pt/Ti top electrode was electron-beam deposited through the nanoporous template, and a solvent-assisted lift-off process was adopted to produce the ordered arrays of nanopatterned top electrodes shown in the SEM image of Figure 2b. We deposited in this step a bilayer structure composed of 4 nm Ti and 6 nm Pt, obtaining the device structure descripted in Figure 2c. The Ti layer was chosen because of his oxygen-reacting property, which was demonstrated to significantly reduce the forming voltage and reduce the device variability. 34,35 Figure 2d shows the sample surface morphology obtained by AFM, where distinct nanodevices with hexagonal distribution are clearly distinguishable. In Figure 2e, a line scan extracted from Figure 2d is shown. The average electrode height of 8±1 nm obtained from AFM data analysis is compatible with the deposited metal thickness, while the electrode size appears larger than in the SEM image (Figure 2b) because of the lateral convolution with the AFM tip geometry.

Due to the oxidation of the TiN upper interface prior to the HfO<sub>2</sub> deposition, an additional TiO<sub>2</sub> oxide layer of roughly 2 nm intermixed with TiO<sub>x</sub>N<sub>y</sub> components was found by XPS analysis (data not shown). This additional oxide layer was reported to increase the LRS resistance, which is

desirable for large array memory architectures.<sup>15</sup> This highly defective interface can additionally accommodate excess oxygen species during the set process, serving as oxygen reservoir for the filament oxidation in the subsequent reset process.<sup>36</sup> Besides, the deposition of a thin 3 nm HfO<sub>2</sub> was chosen in order to lower the operation voltages, as required for RS device scaling.<sup>37,38</sup>

**Figure 2.** SEM plane views of (a) nanoporous PS template obtained by BCP self-assembling in periodic perpendicular cylinders and (b) arrays of Pt/Ti top electrodes on top of the HfO<sub>2</sub> surface obtained from the self-assembled polymeric template depicted in (a). (c) Device stack representation. (d) AFM surface morphology showing the top electrodes with hexagonal distribution and relative line scan (e) displaying the electrodes height.

*Initial state characterization of the nanoscale devices*

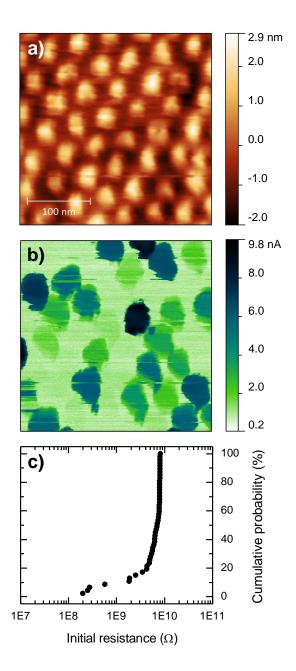

Figure 3a and 3b display simultaneously acquired C-AFM topographic and current maps for the characterization of the initial leakage conductance of the devices. A potential difference of 1.5 V

was chosen to highlight the device variability, yet low enough to avoid electric field-induced perturbations, as verified with repeated scans. A close correlation can be found between the hexagonally packed Pt/Ti metal electrodes in Figure 3a and the uniform conductive spots in Figure 3b, confirming the equipotential behavior of the nanometer-sized metal electrodes, which is the first requirement for their correct operation. We noticed however very different leakage current levels among different devices. By plotting the cumulative distribution of the initial state resistances, two different conditions can be defined in Figure 3c. While nearly 80% of the devices with higher resistance show a very low dispersion, around 20% of the remaining devices in the lower resistance distribution tail have a conductance spread over almost 2 decades. Repeating the initial state analysis in a different area of the sample and with a different voltage, the same general trend was obtained (Figure S1).

**Figure 3.** AFM morphology (a) and corresponding current map (b) of top metal electrodes defined by BCP lithography on the HfO<sub>2</sub> surface, acquired with an applied bias of 1.5 V. (c) Initial state resistance distribution of the devices in figure (b).

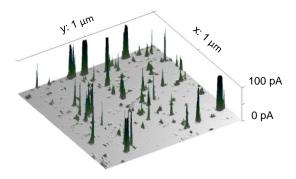

In order to investigate the device initial state variability, we assessed the oxide non-homogeneity at the nanoscale by acquiring current maps of the bare HfO<sub>2</sub>/TiN film surface, before top electrode patterning, using the conductive AFM tip as top electrode (Figure 4). The majority of the HfO<sub>2</sub>

film is highly insulating and presents a leakage current below the detection limit. This finding correlates well with the 80% of highly resistive devices reported in Figure 3. Additionally, leaky sites in HfO<sub>2</sub> are randomly spread, with a current level that differs greatly between the different sites.<sup>39</sup> This is likely the cause of the resistance variability over 2 decades for the 20% of the most conductive nanodevices, probably located in correspondence of leaky conduction paths. This C-AFM electrical characterization of the bare oxide is in agreement with what is in general observed for amorphous 3 nm HfO<sub>2</sub> samples.<sup>40,41</sup> We observed an average number of 100 spots/μm<sup>2</sup> at 1.5 V, a value in agreement with previous observations<sup>40</sup>. Comparing this value with the density of 500 devices/μm<sup>2</sup> in the sample with BCP patterned electrodes, we can clearly correlate the 20% of highly conductive devices with the inherent presence of leakage current paths in the bare HfO<sub>2</sub>/TiN stack.

**Figure 4.** C-AFM current map of a 3 nm HfO<sub>2</sub>/TiN bare surface acquired at 1.5 V bias displaying the film nanoscale conductance variability.

### Nanoscale device RS operations

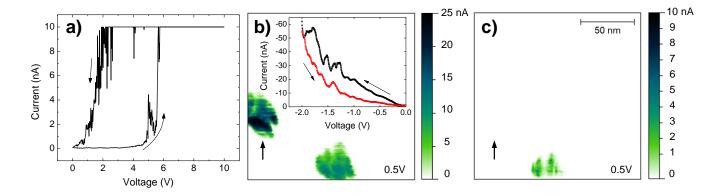

With the sharp conductive tip of the AFM, we achieved a selective addressing of individual nanoscaled memory cells. By placing the tip over a selected electrode and ramping the voltage, the forming transition can be obtained (Figure 5a). We repeated the operation on different randomly

selected devices, finding forming voltages comprised in the 4.5 - 5.5 V range. This transition can be obtained regardless of the device initial resistance status, meaning that the inherent presence of leakage conduction paths is not a prerequisite for the device forming. When using a direct AFM tip contact (Pt-Ir coated tip as top electrode), previous works on 3 nm HfO<sub>2</sub> amorphous films point out that quite a high voltage (>16 V) is necessary to induce the oxide breakdown. 40,41 Indeed, acquiring voltage scans over the HfO<sub>2</sub>/TiN bare surface in 25 random positions, no forming transition in the 0-10 V range was obtained, locating the tip in areas showing either leaky sites or low initial conduction (see Figure S2). In comparison with a direct AFM tip contact, the nanoscale electrical characterization of the RS system using nanoelectrodes defined by BCP lithography brings the big advantage that real devices are investigated. In this way, various artifacts located at the oxide – electrode interface can be avoided (water meniscus, anodic oxidation, etc.), 42 while the device area can be carefully defined by the BCP template and the electrode material can be more easily selected. In this respect, the insertion if the Ti interlayer in the top electrode stack allowed to exploit the Ti oxygen scavenging effect, which was previously associated with a visible reduction of the forming voltage. 34,35,43

**Figure 5.** High initial resistance device (a): Forming process in a Pt/Ti/HfO<sub>2</sub>/TiN nanodevice. 10 nA is the maximum detectable current. Initially leaky devices (c) and (d): Current maps acquired

at 0.5 V before and after the reset operation (inset) of the device indicated by the arrow. After reset, this device is not anymore visible in the reading current map (d).

Considering devices located in correspondence of leaky sites, their higher initial conductance can be manipulate with bipolar voltage operations. In Figure 5b, a current map acquired at 0.5V shows in the scanned area two devices with high initial conductance. Selecting the device indicated by an arrow and performing a steady state negative voltage sweep (inset of Figure 5b), the device conductance is suppressed, as it is evident in the subsequent reading current map of the same area (Figure 5c). This can be interpreted as the reset of a device that is initially in a LRS, with the conductive channel already in place without the requirement of an initial forming step.

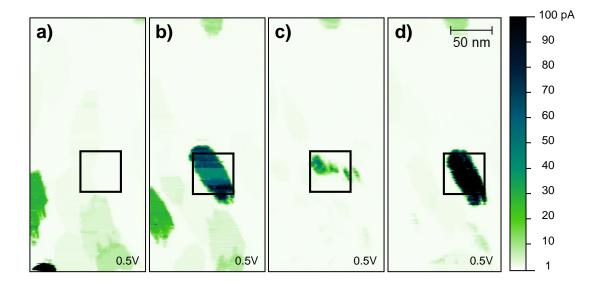

Owing to the small electrode dimension, which is of the same order of magnitude of the tip contact area, a different C-AFM procedure was developed to gain better reproducibility during repeated set/reset processes. By scanning the tip over only one selected device with a constant applied bias, we improved the tip – electrode contact, while the applied bias was chosen high enough to induce the RS phenomenon. The induced conductance modification was then inspected with a following reading current map over a larger area at a low non-perturbing voltage. The result of this switching procedure is reported in the series of reading current maps of Figure 6. In Figure 6a, a current map displays the initial resistance status of the devices. The AFM tip was then scanned with a constant bias of +4 V over the area enclosed by the black square (50 nm side), containing a single device which exhibits an initial current level below the ammeter sensitivity but was visible in the related topographic map (not shown). The subsequent current map of the whole area (Figure 6b) shows a significant conductance increase of the device under test (forming process). The voltage required to induce the forming transition was is in this case slightly lower than that required for punctual AFM tip operations as in Figure 5a, thanks to the longer lasting

voltage stress induced with scanning tip operations, along with a more stable tip – electrode contact that helps reducing the contact series resistance. Scanning again over the same device with -3V, we substantially suppressed the conductivity (reset), as visible in Figure 6c, while with the application of +4 V we were able to restore the low resistance state (Figure 6d). It is worth noting that the reading current maps were acquired about 10 minutes after the switching occurred, indicating a non-volatile switching in resistance.

**Figure 6.** Current maps (0.5 V bias) acquired before the switching processes (a), after the set process with +4 V (b), after reset with -3 V (c), and after set with +4 V (d). The black square, containing a single nanodevice, encloses the area where the tip was scanned with +4 V/-3 V to induce the set/reset transitions. The elongated shape of the metal electrodes is an artifact caused by a drift in the scanning system.

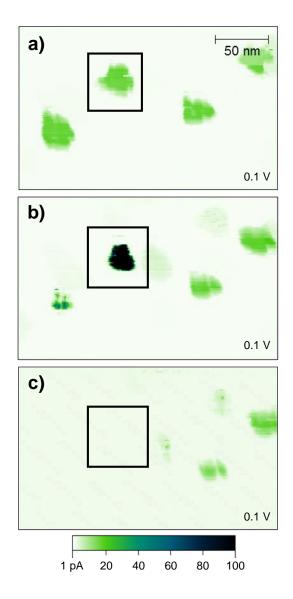

The same operation was also performed in the series of current maps reported in Figure 7 on a device that exhibited a not negligible initial state leakage current, as evident in Figure 7a. However, we noted that after the application of +4 V to the area enclosed by the black square, in Figure 7b we were able to increase the device conductivity to a level comparable with the one of the device

selected in Figures 6b and 6d, regardless of the initial device variability. Moreover, by applying - 4.5 V, we were able to annihilate the conduction path and reach a resistance value lower than the initial state, with a final current value under the detection limit (Figure 7c). The complete reset highlights the high control on the HRS that can be attained with nanosize devices, which is at the basis of the ON/OFF window opening previously observed in nanoscale systems.<sup>38</sup>

In Figure 7, another interesting aspect is visualized. The two conductive devices on the left side of Figure 7a, even if not nearest neighbors, share the same initial current value of 15 pA. After the application of a potential difference to the device enclosed by the black square, the not selected device at the bottom left was also influenced. This cross-talk effect between distinct devices at a distance of 75 nm was obtained again during the reset operation, when both devices reached a resistance value higher than the initial state. It is worth noting that another device is located in between the considered electrodes, which was unaffected during both set and reset operations, demonstrating that the observed cross-talk cannot be ascribed to the tip contacting neighboring devices at the same time. Two other devices visible in Figure 7 at a distance of 80 nm and 130 nm were also unaffected, while a slight lowering in their conductance from Figure 7a to Figure 7c can be ascribed to the tip coating wearing out.

**Figure 7.** Current maps (0.1 V bias) acquired before the bipolar voltage operation (a), after set (b), and after complete reset (c). To induce the set and reset processes, the tip was scanned in the area enclosed by the black squares with a constant applied bias of +4 V (set) and -4.5 V (reset).

A similar cross-talk phenomenon was previously reported in the bare HfO<sub>2</sub>/TiN stack using the conducting AFM tip as a mobile top electrode scanning the surface. After forming, distinct conductive spots appeared in the scanned region, while the afterward reset of one spot influenced the neighboring ones. The observed phenomenon was explained with the formation of bunches of

connected conductive filaments during forming.<sup>39</sup> In the present case, we adopted an array of fixed devices instead of a mobile scanning electrode, with the AFM tip contacting only one device during forming. The presence of connected filaments should therefore be intrinsic of the HfO<sub>2</sub>/TiN stack, as also indicated by the reinforcement of both devices after forming in Figure 7b.

#### DISCUSSION

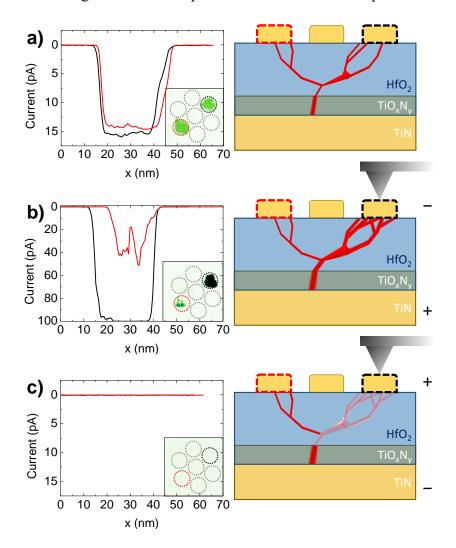

Starting from the experimental evidences, we propose a model to explain the observed phenomenon. In Figure 8, we relate the line scans of the correlated devices (snapshots of the current maps of Figure 7 are reported as insets) with a pictorial view of the proposed model. Starting from Figure 8a, since the two devices show an initial conduction level higher than the neighboring devices, there must be leaky conductions path already in place in the HfO<sub>2</sub> film. As a positive potential difference is applied between the common bottom electrode and the selected top electrode (Figure 8b), the filament gets reinforced due to oxygen vacancies formation and migration in the filament region<sup>44,45</sup>. Since this process leads to a conductance increase of both the selected and unselected devices, they are likely to share a common portion of the filamentary conduction path. The final current level of the not selected device is however lower than that of the selected device, meaning that only a small branch of the filament region as oxygen vacancies migrate toward the bottom electrode and the filament is oxidized, interrupting the conduction path for both the considered devices.

Even if the experimental results suggest the existence of connected filamentary conduction paths, their exact localization is not straightforward. As suggested by Brivio *et al.*<sup>39</sup>, the origin of the localized conduction paths can be located at the highly defective HfO<sub>2</sub>/TiN interface, with the TiN surface roughness also likely to play a role. Even though the filaments should extend

throughout the oxide film thickness, its amorphous structure excludes the presence of grain boundaries as fast diffusion paths for the oxygen vacancies, leaving room for additional investigations in order to get a further comprehension of the described phenomenon.

**Figure 8.** Schematic model of the correlated switching for two different devices. Three top electrodes are represented, being part of a periodic electrodes array with hexagonal distribution, as represented in the insets of (a)-(c) with dotted circles. On the left, line scans of the device to which the bias was applied (black) and of the other correlated device (red) before the bipolar voltage operations (a), after set (b), and after full reset (c). On the right, a pictorial view illustrates the proposed cross-talk mechanism.

Thermal profile simulations recently pointed out the thermal cross-talk, rather than the filament size itself, to be the ultimate limit for device scaling. We however can exclude thermal cross-talk to be the cause of linked switching behavior in our system. Indeed, a second neighboring device was affected, while no nearest neighbor was influenced. Additionally, the cross-talk phenomenon appeared also during the set transition, which is mostly electric field-induced and not a purely thermal process. Additional investigation is required to verify whether thermal effects could be detrimental for data retention in our high-density array.

The observed cross-talk phenomenon is expected to occur only in applications based on a continuous switching medium. The integration of a continuous oxide film is however of crucial importance in many recent prototype applications of highly scaled ReRAM devices, based on both planar technology<sup>37</sup> or on a three-dimensional integration<sup>15,16,47</sup>. In the latter case in particular, the near proximity of the stacked cells make them particularly vulnerable to the cross-talk issue and it must be considered during the structure design. While the oxide patterning would provide a possible solution, it is responsible for a variety of additional issues related to the etching procedure and encapsulation<sup>14</sup>, and is hardly applicable in case of stacked integration of vertical ReRAM devices.

#### CONCLUSIONS

A bottom-up fabrication approach based on BCP self-assembling allowed the fabrication of an ordered array of Pt/Ti/HfO<sub>2</sub>/TiN resistive switching memory devices with a well-controlled diameter of 28 nm and a density of 5x10<sup>10</sup> devices/cm<sup>2</sup>, with further device downscaling possible. The bilayer Pt/Ti top metal electrodes were contacted using C-AFM, allowing a characterization of the device initial state variability, which was correlated with the inherent presence of the leakage current paths randomly spread in the HfO<sub>2</sub>/TiN stack. The bipolar RS operation was confirmed for

the produced nanoscale devices, with a forming voltage lower than what is in general observed with the direct adoption of the AFM tip as top electrode. Owing to the high density of the nanodevices under study, we observed a cross-talk between two different memory cells at a distance of 75 nm, posing a potential issue for highly scaled, high-density memory applications based on continuous HfO<sub>2</sub> films. We ascribed the observed cross-talk to filamentary conduction paths in the oxide film, with different devices sharing a common portion of the filament.

#### **METHODS**

Substrate cleaning and bottom electrode processing. n<sup>++</sup> Si wafers were cleaned by standard SC-2 (HCl:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O 1:1:5 solution) cleaning procedure; the native oxide was removed by 10s dip in HF solution (1:50), resulting in H-terminated Si. 10 nm Ti adhesion layer and 40 nm TiN as back electrode were afterward deposited by sputter deposition (100W RF power; 40 sccm Ar and 40sccm Ar/4sccm N<sub>2</sub> flux for the Ti and TiN depositions, respectively)

*ALD HfO*<sub>2</sub> oxide deposition. A 3 nm thick HfO<sub>2</sub> film was deposited on the bottom electrode by atomic layer deposition using Bis(methylcyclopentadienyl)methoxymethylhafnium(IV) (HfD-O4) and H<sub>2</sub>O as precursors in the Savannah 200 ALD reactor (Cambridge Nanotech. Inc.) at 300°C substrate temperature.<sup>48,49</sup> Film thickness and dielectric properties were monitored by spectroscopic ellipsometry (Woolliam, Inc.).

Brush layer and block copolymer deposition. Samples were sonicated in an isopropanol bath prior to polymer deposition to remove particles contamination. A hydroxyl-terminated Poly(Styrene-r-Methyl methacrylate) random copolymer with molecular weight  $M_n = 14 \text{ kg mol}^{-1}$ , Styrene fraction f 0.62 and polydispersivity index PDI 1.09 in a toluene solution (9 mg in 1 ml) was spun at 3000 rpm for 30s on the HfO<sub>2</sub> substrate for substrate neutralization and annealed at 310°C for 10min dwell time in an RTP machine (20°C s<sup>-1</sup> ramp) in N<sub>2</sub> ambient (1000 sccm). A 5

min toluene bath removed the ungrafted polymer chains. A film of Polystyrene-b-Polymethylmethacrylate BCP (Polymer Source Inc.) was afterward spun on the neutralized surface. A toluene solution (9 mg in 1 ml) was used ( $M_n$  101.5 kg mol<sup>-1</sup>, f 0.67, PDI 1.07), spun on the surface at 3000 rpm for 30s. The self-assembling was promoted with a 250°C RTP annealing for 5 min in N<sub>2</sub> ambient. The final nanoporous PS template was obtained by removing the PMMA component with UV (5 mW cm<sup>-2</sup>,  $\lambda$  253.7 nm) for 15 min followed by a 100% acetic acid etch for 8 min, rinsing in water and drying in N<sub>2</sub> flow and a final oxygen plasma treatment at 40 W for a total of 130s.

Images of the samples surface were acquired with a FE-SEM (Supra 40, Carl Zeiss) at 15 kV using the in-lens detector.

Top electrodes nanopatterning. A film of 4 nm Ti / 6 nm Pt was deposited by electron-beam deposition on top of the nanoporous PS template, with a chamber pressure lower than  $2 \cdot 10^{-6}$  mbar. The lift-off process was carried out in warm toluene (80°C, sonication bath).  $^{19,27,28}$

AFM electrical and morphological characterization. A Dimension Edge instrument (Bruker) equipped with a TUNA electrometer (1 pA – 1 μA current range) was used in combination with highly doped diamond-coated tips (CDT-CONTR, nanosensor, with 100-200 nm curvature radius but a nanoroughness in the 10 nm regime, lowering the contact area) or Pt/Ir coated tips (PPP-CONTPt, nanosensor, with a 25 nm thick coating on top of a <10 nm curvature radius tip). The bias voltage was applied to the substrate, while the tip was held grounded.

#### ASSOCIATED CONTENT

**Supporting Information**. Initial state conductance and device variability for two different sample areas; forming operations attempted using the Pt-Ir AFM tip as top electrode. This material is available free of charge via the Internet at http://pubs.acs.org.

#### **AUTHOR INFORMATION**

#### **Corresponding Author**

\*(Word Style "FA Corresponding Author Footnote"). \* (Word Style

"FA\_Corresponding\_Author\_Footnote"). Give contact information for the author(s) to whom correspondence should be addressed.

#### **Present Addresses**

†If an author's address is different than the one given in the affiliation line, this information may be included here.

#### **Author Contributions**

The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript. ‡These authors contributed equally. (match statement to author names with a symbol)

#### **Funding Sources**

Any funds used to support the research of the manuscript should be placed here (per journal style).

#### **Notes**

Any additional relevant notes should be placed here.

#### **ACKNOWLEDGMENT**

(Word Style "TD\_Acknowledgments"). Generally the last paragraph of the paper is the place to acknowledge people, organizations, and financing (you may state grant numbers and sponsors here). Follow the journal's guidelines on what to include in the Acknowledgments section.

#### **ABBREVIATIONS**

CCR2, CC chemokine receptor 2; CCL2, CC chemokine ligand 2; CCR5, CC chemokine receptor 5; TLC, thin layer chromatography.

#### **REFERENCES**

- (1) Kim, H.-C.; Park, S.-M.; Hinsberg, W. D. Block Copolymer Based Nanostructures: Materials, Processes, and Applications to Electronics. *Chem. Rev.* **2010**, *110*, 146–177.

- (2) Bang, J.; Jeong, U.; Ryu, D. Y.; Russell, T. P.; Hawker, C. J. Block Copolymer Nanolithography: Translation of Molecular Level Control to Nanoscale Patterns. *Adv. Mater.* **2009**, *21*, 4769–4792.

- (3) Waser, R.; Aono, M. Nanoionics-Based Resistive Switching Memories. *Nat. Mater.* **2007**, *6*, 833–840.

- (4) Linn, E.; Rosezin, R.; Kügeler, C.; Waser, R. Complementary Resistive Switches for Passive Nanocrossbar Memories. *Nat. Mater.* **2010**, *9*, 403–406.

- (5) Jeong, D. S.; Thomas, R.; Katiyar, R. S.; Scott, J. F.; Kohlstedt, H.; Petraru, A.; Hwang,

C. S. Emerging Memories: Resistive Switching Mechanisms and Current Status. *Rep. Prog. Phys.*2012, 75, 076502.

- (6) Waser, R.; Dittmann, R.; Staikov, G.; Szot, K. Redox-Based Resistive Switching Memories Nanoionic Mechanisms, Prospects, and Challenges. *Adv. Mater.* **2009**, *21*, 2632–2663.

- (7) Yang, J. J.; Pickett, M. D.; Li, X.; Ohlberg, D. A. A.; Stewart, D. R.; Williams, R. S. Memristive Switching Mechanism for Metal/oxide/metal Nanodevices. *Nat. Nanotechnol.* **2008**, *3*, 429–433.

- (8) Kim, S.; Choi, S.; Lu, W. Comprehensive Physical Model of Dynamic Resistive Switching in an Oxide Memristor. *ACS Nano* **2014**, *8*, 2369–2376.

- (9) Sawa, A. Resistive Switching in Transition Metal Oxides. *Mater. Today* **2008**, *11*, 28–36.

- (10) Yoon, J. H.; Song, S. J.; Yoo, I.-H.; Seok, J. Y.; Yoon, K. J.; Kwon, D. E.; Park, T. H.; Hwang, C. S. Highly Uniform, Electroforming-Free, and Self-Rectifying Resistive Memory in the Pt/Ta<sub>2</sub>O<sub>5</sub>/HfO<sub>2-x</sub>/TiN Structure. *Adv. Funct. Mater.* **2014**, *24*, 5086–5095.

- (11) Chen, Y. Y.; Goux, L.; Pantisano, L.; Swerts, J.; Adelmann, C.; Mertens, S.; Afanasiev, V. V.; Wang, X. P.; Govoreanu, B.; Degraeve, R. Fully CMOS BEOL Compatible HfO2 RRAM Cell, with Low (μA) Program Current, Strong Retention and High Scalability, Using an Optimized Plasma Enhanced Atomic Layer Deposition (PEALD) Process for TiN Electrode. In *Interconnect Technology Conference and 2011 Materials for Advanced Metallization (IITC/MAM)*, 2011 IEEE International. 2011, 1–3.

- (12) Privitera, S.; Bersuker, G.; Butcher, B.; Kalantarian, A.; Lombardo, S.; Bongiorno, C.; Geer, R.; Gilmer, D. C.; Kirsch, P. D. Microscopy Study of the Conductive Filament in HfO<sub>2</sub> Resistive Switching Memory Devices. *Microelectron. Eng.* **2013**, *109*, 75–78.

- (13) Celano, U.; Goux, L.; Belmonte, A.; Opsomer, K.; Franquet, A.; Schulze, A.; Detavernier, C.; Richard, O.; Bender, H.; Jurczak, M.; *et al.* Three-Dimensional Observation of the Conductive Filament in Nanoscaled Resistive Memory Devices. *Nano Lett.* **2014**, 2406-2406.

- (14) Kar, G. S.; Fantini, A.; Chen, Y.-Y.; Paraschiv, V.; Govoreanu, B.; Hody, H.; Jossart, N.; Tielens, H.; Brus, S.; Richard, O.; *et al.* Process-Improved RRAM Cell Performance and Reliability and Paving the Way for Manufacturability and Scalability for High Density Memory Application. In *2012 Symposium on VLSI Technology (VLSIT)* **2012**, 157–158.

- (15) Yu, S.; Chen, H.-Y.; Gao, B.; Kang, J.; Wong, H.-S. P. HfOx-Based Vertical Resistive Switching Random Access Memory Suitable for Bit-Cost-Effective Three-Dimensional Cross-Point Architecture. *ACS Nano* **2013**, *7*, 2320–2325.

- (16) Gao, B.; Bi, Y.; Chen, H.-Y.; Liu, R.; Huang, P.; Chen, B.; Liu, L.; Liu, X.; Yu, S.; Wong, H.-S. P.; *et al.* Ultra-Low-Energy Three-Dimensional Oxide-Based Electronic Synapses for Implementation of Robust High-Accuracy Neuromorphic Computation Systems. *ACS Nano* **2014**, *8*, 6998–7004.

- (17) Tallegas, S.; Baron, T.; Gay, G.; Aggrafeil, C.; Salhi, B.; Chevolleau, T.; Cunge, G.; Bsiesy, A.; Tiron, R.; Chevalier, X.; *et al.* Block Copolymer Technology Applied to Nanoelectronics. *Phys. Status Solidi C* **2013**, *10*, 1195–1206.

- (18) Perego, M.; Andreozzi, A.; Vellei, A.; Lupi, F. F.; Seguini, G. Collective Behavior of Block Copolymer Thin Films within Periodic Topographical Structures. *Nanotechnology* **2013**, *24*, 245301.

- (19) Shin, K.; Leach, K. A.; Goldbach, J. T.; Kim, D. H.; Jho, J. Y.; Tuominen, M.; Hawker, C. J.; Russell, T. P. A Simple Route to Metal Nanodots and Nanoporous Metal Films. *Nano Lett.* **2002**, *2*, 933–936.

- (20) Hong, A. J.; Liu, C.-C.; Wang, Y.; Kim, J.; Xiu, F.; Ji, S.; Zou, J.; Nealey, P. F.; Wang, K. L. Metal Nanodot Memory by Self-Assembled Block Copolymer Lift-Off. *Nano Lett.* **2010**, *10*, 224–229.

- (21) Jung, Y. S.; Chang, J. B.; Verploegen, E.; Berggren, K. K.; Ross, C. A. A Path to Ultranarrow Patterns Using Self-Assembled Lithography. *Nano Lett.* **2010**, *10*, 1000–1005.

- (22) Nunns, A.; Gwyther, J.; Manners, I. Inorganic Block Copolymer Lithography. *Polymer* **2013**, *54*, 1269–1284.

- (23) Tsai, H.; Pitera, J. W.; Miyazoe, H.; Bangsaruntip, S.; Engelmann, S. U.; Liu, C.-C.; Cheng, J. Y.; Bucchignano, J. J.; Klaus, D. P.; Joseph, E. A.; *et al.* Two-Dimensional Pattern Formation Using Graphoepitaxy of PS-b-PMMA Block Copolymers for Advanced FinFET Device and Circuit Fabrication. *ACS Nano* **2014**, *8*, 5227–5232.

- (24) Shin, D. O.; Mun, J. H.; Hwang, G.-T.; Yoon, J. M.; Kim, J. Y.; Yun, J. M.; Yang, Y.-B.; Oh, Y.; Lee, J. Y.; Shin, J.; *et al.* Multicomponent Nanopatterns by Directed Block Copolymer Self-Assembly. *ACS Nano* **2013**, *7*, 8899–8907.

- (25) Park, W. I.; You, B. K.; Mun, B. H.; Seo, H. K.; Lee, J. Y.; Hosaka, S.; Yin, Y.; Ross, C. A.; Lee, K. J.; Jung, Y. S. Self-Assembled Incorporation of Modulated Block Copolymer Nanostructures in Phase-Change Memory for Switching Power Reduction. *ACS Nano* **2013**, *7*, 2651–2658.

- (26) Wu, Y.; Yi, H.; Zhang, Z.; Jiang, Z.; Sohn, J.; Wong, S.; Wong, H.-S. P. First Demonstration of RRAM Patterned by Block Copolymer Self-Assembly. In *Electron Devices Meeting (IEDM)*, 2013 IEEE International **2013**, 20.8.1–20.8.4.

- (27) Xiao, S.; Yang, X.; Edwards, E. W.; La, Y.-H.; Nealey, P. F. Graphoepitaxy of Cylinder-Forming Block Copolymers for Use as Templates to Pattern Magnetic Metal Dot Arrays. *Nanotechnology* **2005**, *16*, S324–S329.

- (28) Shin, D. O.; Jeong, J.-R.; Han, T. H.; Koo, C. M.; Park, H.-J.; Lim, Y. T.; Kim, S. O. A Plasmonic Biosensor Array by Block Copolymer Lithography. *J. Mater. Chem.* **2010**, *20*, 7241–7247.

- (29) Mansky, P. Controlling Polymer-Surface Interactions with Random Copolymer Brushes. *Science* **1997**, *275*, 1458–1460.

- (30) Jeong, S.-J.; Xia, G.; Kim, B. H.; Shin, D. O.; Kwon, S.-H.; Kang, S.-W.; Kim, S. O. Universal Block Copolymer Lithography for Metals, Semiconductors, Ceramics, and Polymers. *Adv. Mater.* **2008**, *20*, 1898–1904.

- (31) Lupi, F. F.; Giammaria, T. J.; Ceresoli, M.; Seguini, G.; Sparnacci, K.; Antonioli, D.; Gianotti, V.; Laus, M.; Perego, M. Rapid Thermal Processing of Self-Assembling Block Copolymer Thin Films. *Nanotechnology* **2013**, *24*, 315601.

- (32) Seguini, G.; Giammaria, T. J.; Lupi, F. F.; Sparnacci, K.; Antonioli, D.; Gianotti, V.; Vita, F.; Placentino, I. F.; Hilhorst, J.; Ferrero, C.; *et al.* Thermally Induced Self-Assembly of Cylindrical Nanodomains in Low Molecular Weight PS-b-PMMA Thin Films. *Nanotechnology* **2014**, *25*, 045301.

- (33) Ferrarese Lupi, F.; Giammaria, T. J.; Seguini, G.; Vita, F.; Francescangeli, O.; Sparnacci, K.; Antonioli, D.; Gianotti, V.; Laus, M.; Perego, M. Fine Tuning of Lithographic Masks through

Thin Films of PS-b-PMMA with Different Molar Mass by Rapid Thermal Processing. *ACS Appl. Mater. Interfaces* **2014**, *6*, 7180–7188.

- (34) Padovani, A.; Larcher, L.; Padovani, P.; Cagli, C.; De Salvo, B. Understanding the Role of the Ti Metal Electrode on the Forming of HfO<sub>2</sub>-Based RRAMs. In *Memory Workshop (IMW)*, 2012 4th IEEE International 2012, 1–4.

- (35) Cabout, T.; Buckley, J.; Cagli, C.; Jousseaume, V.; Nodin, J.-F.; de Salvo, B.; Bocquet, M.; Muller, C. Role of Ti and Pt Electrodes on Resistance Switching Variability of HfO<sub>2</sub>-Based Resistive Random Access Memory. *Thin Solid Films* **2013**, *533*, 19–23.

- (36) Yoon, J.-W.; Yoon, J. H.; Lee, J.-H.; Hwang, C. S. Impedance Spectroscopic Analysis on Effects of Partial Oxidation of TiN Bottom Electrode and Microstructure of Amorphous and Crystalline HfO<sub>2</sub> Thin Films on Their Bipolar Resistive Switching. *Nanoscale* **2014**, *6*, 6668–6678.

- (37) Govoreanu, B.; Kar, G. S.; Chen, Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Radu, I. P.; Goux, L.; Clima, S.; Degraeve, R.; *et al.* 10x10nm<sup>2</sup> Hf/HfO<sub>x</sub> Crossbar Resistive RAM with Excellent Performance, Reliability and Low-Energy Operation. In *Electron Devices Meeting* (*IEDM*), 2011 IEEE International **2011**, 31.6.1–31.6.4.

- (38) Goux, L.; Fantini, A.; Degraeve, R.; Raghavan, N.; Nigon, R.; Strangio, S.; Kar, G.; Wouters, D. J.; Chen, Y. Y.; Komura, M.; *et al.* Understanding of the Intrinsic Characteristics and Memory Trade-Offs of Sub-μA Filamentary RRAM Operation. In *2013 Symposium on VLSI Technology (VLSIT)* **2013**, T162–T163.

- (39) Brivio, S.; Tallarida, G.; Cianci, E.; Spiga, S. Formation and Disruption of Conductive Filaments in a HfO<sub>2</sub>/TiN Structure. *Nanotechnology* **2014**, *25*, 385705.

- (40) Lanza, M.; Bersuker, G.; Porti, M.; Miranda, E.; Nafría, M.; Aymerich, X. Resistive Switching in Hafnium Dioxide Layers: Local Phenomenon at Grain Boundaries. *Appl. Phys. Lett.* **2012**, *101*, 193502.

- (41) Lanza, M.; Zhang, K.; Porti, M.; Nafría, M.; Shen, Z. Y.; Liu, L. F.; Kang, J. F.; Gilmer, D.; Bersuker, G. Grain Boundaries as Preferential Sites for Resistive Switching in the HfO<sub>2</sub> Resistive Random Access Memory Structures. *Appl. Phys. Lett.* **2012**, *100*, 123508.

- (42) Lee, H.; Kim, H.; Van, T. N.; Kim, D.-W.; Park, J. Y. Nanoscale Resistive Switching Schottky Contacts on Self-Assembled Pt Nanodots on SrTiO<sub>3</sub>. *ACS Appl. Mater. Interfaces* **2013**, 5, 11668–11672.

- (43) Goux, L.; Wang, X. P.; Chen, Y. Y.; Pantisano, L.; Jossart, N.; Govoreanu, B.; Kittl, J. A.; Jurczak, M.; Altimime, L.; Wouters, D. J. Roles and Effects of TiN and Pt Electrodes in Resistive-Switching HfO<sub>2</sub> Systems. *Electrochem. Solid-State Lett.* **2011**, *14*, H244–H246.

- (44) Ielmini, D.; Nardi, F.; Balatti, S. Evidence for Voltage-Driven Set/Reset Processes in Bipolar Switching RRAM. *IEEE Trans. Electron Devices* **2012**, *59*, 2049–2056.

- (45) Nardi, F.; Larentis, S.; Balatti, S.; Gilmer, D. C.; Ielmini, D. Resistive Switching by Voltage-Driven Ion Migration in Bipolar RRAM–Part I: Experimental Study. *IEEE Trans. Electron Devices* **2012**, *59*, 2461–2467.

- (46) Lohn, A. J.; Mickel, P. R.; Marinella, M. J. Analytical Estimations for Thermal Crosstalk, Retention, and Scaling Limits in Filamentary Resistive Memory. *J. Appl. Phys.* **2014**, *115*, 234507.

- (47) Yu, S.; Chen, H.-Y.; Deng, Y.; Gao, B.; Jiang, Z.; Kang, J.; Wong, H.-S. P. 3D Vertical RRAM Scaling Limit Analysis and Demonstration of 3D Array Operation. In *2013 Symposium on VLSI Technology (VLSIT)* **2013**, T158–T159.

- (48) Cianci, E.; Molle, A.; Lamperti, A.; Wiemer, C.; Spiga, S.; Fanciulli, M. Phase Stabilization of Al:HfO<sub>2</sub> Grown on InxGa1–xAs Substrates (x = 0, 0.15, 0.53) via Trimethylaluminum-Based Atomic Layer Deposition. *ACS Appl. Mater. Interfaces* **2014**, *6*, 3455–3461.

- (49) Spiga, S.; Driussi, F.; Lamperti, A.; Congedo, G.; Salicio, O. Effects of Thermal Treatments on the Trapping Properties of HfO<sub>2</sub> Films for Charge Trap Memories. *Appl. Phys. Express* **2012**, *5*, 021102.